����Ƕ��ʽ�������ߵķ���

������Ƭ��ʵ���ҷ���ʵ������һ����Altera Cyclone �ͺŵ�Niosʵ����,�о���ˬ,�Ͻ�ץס����ѧϰһ��.

ԭ������: http://blog.csdn.net/awgn/archive/2006/01/05/571576.aspx

ARM RealView 2.2 (�������)

���ص�ַ��http://www.9iv.com/down/soft/274.htm?eid=217990

http://lib.verycd.com/2005/11/07/0000073497.html

ȫ����ARM RealView Developer Suite 2.2 ���������棡

ǿ���������ơ�ARM���ɿ������ߡ�Ƕ��ʽϵͳ���

ARM���ȿ�����Ϊ��һ����˾�����֣�Ҳ������Ϊ�Ƕ�һ����������ͨ�ƣ���������Ϊ��һ�ּ��������֡�ARM RealView DEVELOPERϵ�а���RealView���������������Ƚ��Ĵ������ɹ��߲�����Cortex-A8�����������Խ������������Ӷ��ܹ��ṩ�ܳ������� �������ױȵĴ����ܶȡ���һ����Ҳ֧��NEONý����źŴ�����չ����ʹ�ÿ������ܹ�ͨ�����������DSP��������Ŀ���������ʵ�ֲ�Ʒ����Ŀ�ķ��ý� �͡����⣬��������֧�������´����������е����ԡ�

ARM RealView�������߰���һ�������ġ����Լ۱ȿ������Թ��ߣ����ڰ뵼��ͨ��32λ��������MCU����Ʒ�������߰���ARM RealView Developer Suiteȫ�����ȵ�16/32λǶ��ʽRISC�����������������ARM������Բ���Intel( XScale(���������������ʩ�����ߺʹ洢�豸���Ƴ�ARM(r) RealView(���������顣�ù������ṩ��ѱ������ɹ��ܣ�ͬʱ�ɽ��Ϳ����ɱ�����ΪΨһ֧������˳ӦARM�ṹ��Intel Xscale�������Ĺ����飬RealView�ܰ���������Ա��ǿӦ�ù��ܡ�

ARM RealView ��������רΪ�й��г����Ƶ�ARM �������߰�����ǿ��ļ��ɿ����������������ı༭/����/���Թ��ܣ�ȫ��֧��ARM7 �ں˵ĸ���ARM оƬ���ÿ���������ARM RealView development solution�������Ż�/�ü�����ר����ӦARM7 �ں˵Ŀ����������������Լ۱���Ӧ�й��г�������

· ������ ISO C/C++�Ż�������

· C++ ��ģ���

· ǿ��ĺ������

· �����ڴ�ӳ�����ô��������������

· ��ѡ GUI������

· ����ģʽ�ķ��ŵ�����(armsd)

· ָ�������

· ������ʽ�����ƹ���

· ����������

· ȫ��������ĵ�

���������������а���C��C++�������һ��ר����Intel Xscale�������ĺ��������������֧��оƬ���ٹ��ܵ�AXD���Գ���JTAG���Խ��棬�Լ���֧�ֿ����װ�(developer board)��ARM Firmware Suite(tm)�̼���װ��

ARM����ϵͳ�г�����Dan Jaskolski˵��“������Ӣ�ض������úܽ��ܣ���֧��˳ӦARM�ṹ��Intel XScale t�����Ŀ��������Ƕ�ARM�ṹ���������⣬ʹ����������������רҵ�۹⣬Ϊ����ARM�����Ľ�������ṩ��������ı������ɺ͵��Թ��ߡ�ȫ�� RealView���������鼯�������б���Ԫ�أ��ܱ��Ͽ��ٶ��߳ɱ�Ч��ؿ���������Intel XScale��������ϵͳ�ͽ��������”

Ӣ�ض����ֳ����㲿���ܾ���Peter Green˵��“Intel XScale�������ܰ���������Ա�ڶ�����棬�����������ʩ�����ߺʹ洢Ӧ�õ����������������ɱ������̿������ڡ�����ARM RealView���������������Ĺ����ṩ����Ҫ��Դ��ʹ������Ա�������ǵ�ƽ̨�м������蹦�ܺͷ���”

ARMΪ�ⷨ�뵼�嶨��RealView��������

Ӣ��ARM��˾�� ����ARMΪ�ⷨ�뵼�幫˾STMicro����ARM® RealView®�������߰���ARM® RealView®�������߰���һ�������ġ����Լ۱ȿ������Թ��ߣ������ⷨ�뵼��ͨ��32λ��������MCU����Ʒ�������߰���ARM RealView Developer Suite™Ϊ�������书�ܿ������ⷨ�뵼���Ʒ����������

ARM��˾����Ƚ������ֲ�Ʒ����Ӧ�ü�����Ӧ�������漰�����ߡ����硢�������֡�Ӱ���������ӡ���ȫӦ�ü��洢 װ�á� ARM�ṩ�㷺�IJ�Ʒ��������16/32λRISC���������������桢��άͼ�δ����������ֵ�Ԫ�⡢Ƕ��ʽ�洢�������衢���������������Լ�ģ����� ���Ӳ�Ʒ�� ARM��˾Эͬ�ڶ༼���������Ϊҵ���ṩ���١��ȶ�������ϵͳ���������

ARM Developer Suite v1.2 (�����ۺϿ���)

���ص�ַ��http://www.9iv.com/down/soft/1080.htm?eid=217990

ARM Developer Suite™ ADS ��ȫ��ʵʱ�����������߰����������ɵĴ����ܶȺ�ִ���ٶ�����ɿ��ٵͼ۵ش���ARM �ṹӦ��ADS�������ֵ�����ARM eXtended Debugger AXD ���¼��ݵ�ARMDebugger for Windows/ARM Debugger for UNIX ��ARM ���ŵ���������AXD ����ӵ�еͰ汾ARM �����������й��ܻ�������ͼ���û������������Ӵ�����������ʾ��ʽ���ͱ༭�Լ�ȫ�������н���ò�Ʒ������RealMonitor™ ������ǰ̨���Ե�ͬʱ�ϵ����沢���ڲ��ж�Ӧ�õ�����¶�д�ڴ���ٵ��Թ���

ARM ��Real-Time Trace™ ��RealMonitor ��Ϊ��Ҫ��ʵʱ���Խ�������ܹ����̿��������ṩ�����������Թ��ܿ������ڴ����Ƕ�봦�����ں˵ĸ���ϵͳоƬSoC ARM ��Real-Time Trace ��Ʒ�������ٵ��Թ���MultiTrace Ƕ��ʽ���ٺ굥Ԫ��Multi-ICE ARM ��RealMonitor����RMTarget™ RMHost™ ��ARM Developer Suite (ADS) �IJ���Ӳ��

Integrator™

Integrator ϵ��������Ч��ϵͳоƬ����ƽ̨����ARM PrimeCell™����������������������Ӳ���ܹ����̲�Ʒ�������ڽ��������ܳɱ��̼�

ARM Firmware Suite™

ARM �̼����Ǹ��ײ�Ӳ����ص�Ӧ�÷�װ����ARM ����ƽ̨��Ѹ�ٽ�������Integrator ������ARM�ں˵�Ӧ�úͲ���ϵͳģ����

ModelGen

ModelGen ����ģ�����Ͽ�����֧�ָ��Ӱ뵼����������ģ����Ƚ���ģ����ΪARM ����ӵ��ARM �ĺ���������ModelGen �ڸ��ַ������ͼ���ƽ̨��ʵ���źŴ���������ʱ��ģ��

Xilinx ISE 8.2i (ǿ����ӿ���)

���ص�ַ��http://www.9iv.com/down/soft/14.htm?eid=217990

http://lib.verycd.com/2005/12/03/0000077793.html forLinux.(X64)

http://lib.verycd.com/2005/04/07/0000045392.html for Windows

http://www.9iv.com/down/soft/19.htm?eid=217990

Xilinx ISE 8.2 ������2006.6���ͷš�ҵ���������Ŀɱ������ƽ������������ʵ���������ܡ����ʹ��������ͳɱ�����������ʡ�

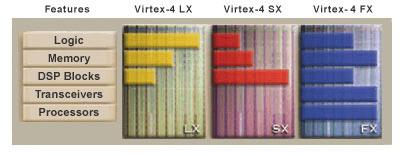

Xilinx ISE 8.2i���˾���Ŀǰ�г��������ٶȣ�Xilinx ISE v8.2i���µ�Virtex-4™ FPGAϵ�л����ж��200,000��������Ԫ�ߴ�500 MHz��Ƶ�����ܣ�ʹ������ܹ�ʵ����ȫո�µ����ǰ��!Xilinx ISE 8.2����������������ʹ�õġ�����һָ��PLD��ƻ������ɶ���FPGA���߹�Ӧ���ṩ�ĸ����������Xilinx ISE 8.2

Xilinx ISE 8.2�ؼ�����

֧��Virtex-4ϵ������ – ҵ���һ����ƽ̨FPGA

����ӽ��ľ�����Ʒ��ȣ�Xilinx Fmax������ƽ�����ܿ��10%-37%��������ܿ��70%��

���Խ�ʡһ�������ٶȵȼ��ijɱ����������������ʵ����͵��ܳɱ���

��֧�ֶദ��������վ��ͨ������������в��ó��̼߳�����ʹ���ܹ���ʡ��Ŀʱ�䲢���ʹ�ù���վ�豸��

�ɱ���������Ժͻ�ù㷺֧�ֵ�ƽ̨

2004��2005��Ķ���������ʾ��ISE��FPGA����ߵ���ѡ��

2006 ��6 �£����������Ƴ������ܻ�ӭ�ļ����������� (ISE) ��ƹ�����8.2i �棬�°汾�������µ� ISE Fmax ������������ǿ�������ۺ������������ Virtex™-4 �� Spartan™-3 �ܹ������ܺ�ʱ���������ԡ�ͨ��ʹ�� ISE 8.2i ����������߿ɽ���������������ǰISE �汾ƽ���߳�10% �� 37%������ȣ�����ʹ�� Virtex-4 FPGA��������������߿ɳ����������������70%��ISE 8.2i ������ҵ��Ψһ�ľֲ������ü�����������ǿ����ʵ�ָ��͵ijɱ�����С�ijߴ���͵Ĺ��ġ�

ͨ���Ե�����һ��ISE �汾�ijɱ����ṩ��ͬ��ƽ���ٶȵȼ�����Щ������ּ�ڽ�һ����ǿ����˼���������ϵͳ��ƵĽ����������������Ƕ��ʽ�����������źŴ���

(DSP) ��������Э��ȹ��ܵ���ơ�ͨ���� ISE ������ʹ�ø������ۺϹ��ܣ�����߿����̶ȵ�������������ʣ��ӿ�����ʱ�䣬�����ܿ����ɱ������⣬����

ChipScope™ Pro 8.2i Ƭ�ڵ��� (in-silicon debug) �����Լ���Ϊǿ��ľֲ�������֧�ֵ����Խ�һ�������˿���ʱ�䣬������ϵͳ�ɱ���

“����һֱ����������Ǻ����Խ�����ǵĹؼ���ս����ʱ���������ɱ���ϵͳ��Ƹ��Ӷȵȡ�ISE 8.2i ͨ������Ʊ����Ż��ܺõؽ������Щ���⣬�ṩ��ʵ���Ե��Զ���

Fmax ������ֱ�۵��½������ԣ�”����˼��˾������������ܲ� Bruce Talley ˵��“��������߿����и���İ��������������ղ�Ʒ��ϵͳ���ܡ������Ժͳɱ�Ŀ�ꡣ”

ISE Fmax ���ܼ����ɽ�����ٶ���������߳�������������� 70%

�µ� ISE Fmax �������ø�Ч�㷨�Ը��������ۺ������Ż��Ľ����ʹ Virtex-4 FPGA ���������ƱȾ������������߳� 70%��ISE Fmax ����������������ض�ʱ��ʱ��������װ�벼�֡����������벼�ֺ����Ż���һ�����ܡ����°汾�а����� ISE Xplorer ������һ������ʹ�õĽű����ɰ���������������Ż� Virtex-4 �� Spartan-3FPGA �����ܣ�����ʱ��������ƿɱ���ǰ�汾ƽ����� 10% �����ܡ�ISE 8.2i �ṩ��һ����������ģʽ���ɶ�û��ʱ��Լ��������ṩ 37% ��ֱ�����ܸ��ơ�

ISE Fmax �������� Synplicity �� Mentor Graphics �ṩ���ۺ��Ż�������Ϊ���䡣�ۺ��Ż������� ISE Fmax �����Ľ�Ͽ�ʹ�û�������̵�ʱ��Ŀ�ꡣ

“�µ� ISE 8.2i ������ Synplify Pro �ۺϼ�����Ʒ�Ľ�ϣ�Ϊ����˼ FPGA ��������ṩ���ƽ�ʱ�����ܵ����ƣ�”Synplicity ��˾ FPGA ��ƷӪ������ Jeff Garrison ˵��“����һֱ������˼���ֽ��ܺ�������ȷ�����ǵ����¼���������������ǵ� Synplify Premier ��Ʒ������Ļ���ͼ�ε������ۺϼ���ȣ?ܹ��?ISE ����ʵ�ֶԽӣ��Ӷ�Ϊ��������˼ FPGA ��Ʒ���ṩ����ʱ��������”

“Mentor Graphics�ĸ� Precision Synthesis �������������˼ ISE 8.2i ���еĽ��ܼ��ɣ�Ϊ���ǵĹ�ͬ�ͻ�ͬʱ�ṩ�����ֻ�����������ԣ�” Mentor Graphics ��˾��ƴ������ۺϼ������ܾ��� Simon Bloch ˵��“Precision Synthesis �о����ͻ���֤����Ʒ�����������ʵ���Զ�/�����Ż����û�����֮���ǡ��ƽ�⣬���ڿ�ΪISE 8.2i ��ҵ�����ȵ�����˼Fmax �����ṩ�������䡣”

ҵ��Ψһ�ľֲ������ý������

ͨ���Ƴ� 8.2i �汾������˼������һ���µķ���������ǿ��ҵ������Ψһ�ľֲ������ý���������ֲ������ÿɽ���ϵͳ�ɱ����ߴ硢�������������ģ��������ڶ��Ӧ�ã��� �������ߵ� (SDR) �����ܼ���ȡ���������ڿ������������ಿ�ּ������е�ͬʱ����ͬ��Ӳ�����ö�̬���ص� FPGA ��ͬһ��������ʵʱ�ɱ�����Խ������ֳ��������ԺͶ����������Ļ����ϡ��ֳ��������ԺͶ����������Ѿ�ʹ��������˼�ͻ�ͨ��ʵʱ���������ϵͳ�ɿ��ԣ� �������ֳ�����ɱ������ӳ����г������в�Ʒ��ʹ��������

�����������������

ISE 8.2i ����������ģʽ���ṩ�˿� 37% �İ�ť����ʵ�ֶ�����Լ������ƽ��п��ٺ����ɵ�������ISE 8.2i ���ṩ�˶�˫�� CPU ����վ��֧�֣���ʵ�ָ���ı���ʱ����ڶ�� CPU ���ϵ������ҵ���д�����ҵ����ȫ��Ĺ��ķ���������� Xpower��WebPower Tools 8.2i �иĽ��� Web ���������Լ��µĹ����Ż�����������һ����ǿ����Щ������ISE 8.2i Project Navigator����Ŀ��������ͼ��ɵ� ISE Simulator��������������������ƽ̨���ṩ��ȫ��ֱ�۵� Windows XPTM ��ۺ��ܣ�ʹ ISE 8.2i ����ǰ�κ�ʱ������ѧϰ��ʹ�á�

ChipScope Pro 8.2i

ChipScope Pro 8.2i �ķ����ṩ��ҵ�������ƺ����õĵ��Խ�����������ɳ�������50 ����ChipScope Pro �ں���Դ�����������û�����Ƭ�ϵ�������֤����ѡ��紥�����ȡ�������ȣ��Լ��������紥������ʹ洢�ʸ����ȣ��Ծ���Ƭ�Ͽ������� FPGA ��Դ����֮������ƽ�⡣

Xilinx EDK 8.2i - Ƕ��ʽ������

http://www.9iv.com/down/soft/385.htm?eid=217990

Xilinxƽ̨FPGA������Virtex-4��Virtex-II Pro ��Spartan-3 ����ϵ�����������ŶӶ������ǵ�Ӳ��/������ƣ����Ż������Լ������ܡ��ߴ�ͳɱ�. �������Ŀɱ��ƽ̨����Щ���ܵ�ƽ̨�����ܹ�ʹϵͳ�ܹ���Ӳ������������ʦ��Ϊ�ɱ��ϵͳ�����ר�ҡ�

XPS 8.1i ֧��Virtex-4 FX������һϵ�к����õĸĽ�

���Ǻܸ��˵��������� 8.1i ��Ƕ��ʽ��������ƽ̨�����ҹ��߰�����Щ����ǿ��Ĵ���������������Xilinx �ۺ���Ƕ��ʽ��������Ĺؼ����֣�����Virtex ��Spartan��FPGA. Xilinx ƽ̨�����ҹ��߰�ͨ����ȡ���Զ���������ϵͳ��ƣ�������Ƕ��ʽ������

8.1i ��Ҫ�ĸ����Ƕ�Virtex-4 FX ƽ̨FPGA����������XPS�Ľ��ṩ�µ����֧�֣���������������������Ӳ��ƽ̨�����ĸĽ��������ԺͲ�Ʒ�ĸĽ���

Xilinx EDK 7.1 (Ƕ��ʽ���)

���ص�ַ��http://www.9iv.com/down/soft/824.htm?eid=217990

Xilinx EDK��һ�����������������Ƕ��ʽ���ϵͳ�Ľ�����������Ԥ���õ���������Platform Studio�����Լ�����Ƕ��ʽIBM PowerPC™ Ӳ���������˺�/��Xilinx MicroBlaze™���������˽���Xilinxƽ̨FPGA���ʱ����ļ����ĵ���IP.

Xilinx EDK 7.1i - Ƕ��ʽ������

Xilinxƽ̨ FPGA������Virtex-4��Virtex-II Pro ��Spartan-3 ����ϵ�����������ŶӶ������ǵ�Ӳ��/������ƣ����Ż������Լ������ܡ��ߴ�ͳɱ�. �������Ŀɱ��ƽ̨����Щ���ܵ�ƽ̨�����ܹ�ʹϵͳ�ܹ���Ӳ������������ʦ��Ϊ�ɱ��ϵͳ�����ר�ҡ�

XPS 7.1i ֧��Virtex-4 FX������һϵ�к����õĸĽ�

���Ǻܸ��˵��������� 7.1i ��Ƕ��ʽ��������ƽ̨�����ҹ��߰�����Щ����ǿ��Ĵ���������������Xilinx �ۺ���Ƕ��ʽ��������Ĺؼ����֣�����Virtex ��Spartan��FPGA. Xilinx ƽ̨�����ҹ��߰�ͨ����ȡ���Զ���������ϵͳ��ƣ�������Ƕ��ʽ������

7.1i ��Ҫ�ĸ����Ƕ�Virtex-4 FX ƽ̨FPGA����������XPS�Ľ��ṩ�µ����֧�֣���������������������Ӳ��ƽ̨�����ĸĽ��������ԺͲ�Ʒ�ĸĽ���7.1i ��Ҫ�������µĴ��£�

Virtex-4 FX ƽ̨FPGAǶ��ʽ����֧��:

ʹ��Э��������Ԫ (APU)��ԪӦ�ã��Ż������ܣ�ͨ������������Ӳ����ǿ����������������/�����ؼ�������ʶ������ƿ����ʹ��ƹ�������FPGA Ӳ�� (XPS-SDK)�ļ���

Ӳ��ƽ̨�����ĸĽ�:

���������Դ����(C, MSS, MHS, etc.)

ISE ��XPS��������- ISEֱ�ӵ���XPS�ij��������ϵͳ�齨����

������ݱ�������

����Ӧ�ò��Դ��������

XPS ���滷�������

ΪXPS�������Ƶİ嶨���ļ�

�����Ժ�������Ʒ�Ľ�

XMD�ĸĽ�

֧���µ�MicroBlaze�������������Т���ظ���

�жϺ�FLASH���Եĸ���ϸ����

FLASH��д����ĸĽ�

�Զ��������س��������

����

XPS���滷�������

�Զ����Ե�����

MicroBlaze ISS֧��/�Ľ�

FSL���ٻ���洢�����ӽӿ�

FSL��������

ģ�͵ĸĽ�

OPB Uartlite ֧���жϡ������ʵ�

OPB GPIO֧���ж�

OPB��ʱ��֧�ֶ����ʱ��

ϵͳ����֧�� (MicroBlaze)

ΪMicroBlazeϵͳ��������ƽ̨ģ��

��Ҫ

������ 8.4��TCL

���� GUI �ͻ������ߵ�������

DRC�ĸĽ�

�������°�GCC������MB��PPC

LWIP & XMK������ڲ�ۣ� Ethernetlite��LWIP֧��

�������ĸĽ�����CMPָ� MB-gcc�Ż�

���ݱ�������

PBDE�ĸĽ�

���������ж˿�

ʹ�˿ڳ�Ϊȫ�ֻ��ⲿ�˿ڵ�����

��ԭ��ͼ����JPEG�ļ���

��FSL����Create IP��

���ڣ�����/������������Verilog������û�����

�Ľ��˿�����û���

֧��Verilog

Altera Quartus II 6.0 (�������):

http://www.9iv.com/down/soft/521.htm?eid=217990

http://lib.verycd.com/2005/12/17/0000080089.html

http://www.9iv.com/down/soft/169.htm?eid=217990for linux

Quartus II ����6.0�����ܺ�Ч���ϴﵽ�����ˮƽ����һ�汾������FPGA��Ӧ���ṩ�ĵ�һ��ʱ���������——TimeQuestʱ������ǣ��ܹ��ܺõ�֧��ҵ�� ��Synopsys���Լ��(SDC)ʱ���ʽ���ð汾��������չ�Ŷ���ƹ��ܣ�����˸��ܶ����Э����Ч�ʡ�

Altera��Quartus II����6.0���ܶ������ʵ���ش�Ľ�

2006��5��9�������—Altera��˾��NASDAQ: ALTR������������ʼ����6.0���Quartus® II�������ð汾��������FPGA��Ӧ���ṩ�ĵ�һ��ʱ���������TimeQuestʱ������ǣ�Ϊҵ���Synopsys���Լ����SDC��ʱ���ʽ �ṩ��Ȼ��ȫ���֧�֡���һ���°汾��������չ���Ŷ���ƹ��ܣ��ܹ���Ч�������ܶ�����Ŷ�֮���Э������Щ�Ľ�ӭ���˵�����ܶ�90nm�����Ҫ��ͬ ʱΪ����ͻ��Ը����ܶ�FPGA�������Լ�Altera��չ��һ��65nm��Ʒϵ�д����˻���

Synopsysս�������ܼ�Lonn Fiance����˵��“FPGA�����Ա��ҵ���SDCʱ��Լ����ʽֱ�Ӷ�ȡ��TimeQuestʱ��������У��ܹ���Ѹ�ٵ�ʵ��ʱ��ƽ�������SDC ��ʽ�������FPGA�����Ա��Ч�ʣ���һ���ٽ���ʱ����֤�����ڰ뵼��ҵ���Ӧ�á�”

Quartus II ����6.0���������ܰ�����

TimeQuestʱ�������

TimeQuestʱ�������——�µ� ASIC����ʱ������ǣ��ܹ���Ȼ��֧��ҵ���SDCʱ��Լ����ʽ��TimeQuestʱ������ǰ������������������������и���ʱ��Լ������ƣ����� ʱ�Ӹ�����ƺ�Դͬ���ӿڣ����ܹ�Ѹ�ٽ��и�ʱ����֤��Quartus II ����6.0�����溬��TimeQuestʱ������ǡ�

���̹����ӿ�——�Ľ����Ŷ����

���̹����ӿ�——�ڶ�������� ������Դ��ʱ��Ԥ�㡣���⣬�����������ù��̹����ӿ�������ģ����ʱ��Լ�����Դﵽ������ܡ���һ�¹���ʹ�Ŷ��ܹ�Э��ʵ�ָ��ܶ�FPGA��ƣ��Ӷ��� ��������ܺ�Ч�ʡ���һ�����ǽ�����Quartus II ����5.0��5.1�״�����Ľ���ʽ������ƻ���֮�ϡ�

������ǿ����

SystemVerilog֧��——����������SystemVerilog���֧�֡�SystemVerilog����˼Ĵ������ͼ�(RTL)��Ƶij���ȼ�����Ѹ�ٵ�ʵ��RTL��ơ�

�Ľ���I/O���Ź滮��——ֱ�Ӷ�Altera®�깦�ܡ�֪ʶ��Ȩ(IP)�������ϣ��Լ������ŵļ��䡣

��չ�İ弶���֧��——����Stratix® II FPGA�������ʱ��Ϊ�������ṩHSPICEģ�ͣ�����ߵ�·�彨ģ��Ч�ʡ�

LogicLock��ǿ——�ṩLogicLockTM��Ա��Դ�˳����ܣ���ijЩ��Դ����(���磬�����źŴ��� (DSP)��Ԫ�� M4K�洢����)����Ƶ�Ԫ��LogicLock�������Զ��˳����Ӷ���������Ч�ʡ�

SignalTap II��������——����Nios® II CPU SignalTap® II�ֽ��������Э����ɶ��Ѷ���Nios II�ڵ㼯��“��ȡ”���Լ�Nios II CPU���Ƿ����壬�Ӷ������ϵͳ������Ч�ʡ�

OS֧��

Windows XP Professional x64 (32λ)——����Quartus II����32λӦ��������Windows XP Professional x64����ϵͳ֧��Quartus II ������64λӲ��/����ƽ̨������32λӦ�����������������ܹ����ʸ���Ĵ洢�����Ӷ���������ܡ�

Red Hat linux Enterprise 4.0——�����ṩ֧�֡�

Nios.II.Development.Kit.Version.5.0��NiosIIǶ��ʽ���������ɿ���������

���ص�ַ��http://lib.verycd.com/2005/12/28/0000082073.html

Altera Nios���

��20 ����90���ĩ���ɱ����������PLD���ĸ��Ӷ��Ѿ��ܹ��ڵ����ɱ��������ʵ������ϵͳ�������ĵ�оƬϵͳ��SOC��������ָ��һ��оƬ��ʵ���û��� ���ϵͳ����ͨ����ָ����Ƭ�ڴ洢������������������������������SOC�D�D��ɱ�̵�оƬϵͳ��SOPC���D�D�ܹ��ṩ����PLD�Ĵ��������� 2000�꣬Altera������Nios������������Altera ExcaliburǶ�봦�����ƻ��е�һ����Ʒ������Ϊҵ���һ��Ϊ�ɱ�����Ż��Ŀ����ô����������IJ�������Nios��������ƻ����Ĺ��̺��漰�ľ� �ߣ��Լ�������ݻ�Ϊһ��SOPC���ߡ�

Altera�������ʶ��������ѿɱ�����Ĺ��е����Ƽ��ɵ�Ƕ�봦�����Ŀ��������У����Ǿͻ�ӵ �зdz��ɹ��IJ�Ʒ������PLD�Ĵ�����ǡǡ����Ӧ����������ԡ�һ�������˴�����֮������߾�“�߱�”����ϵ�ṹ���ɷ���ʹ�á���ΪPLD��Ƕ�봦���� �漴����Ч�ˣ��������Ͽ�ʼ�������ԭ�͡�CPU�ܱߵ�ר��Ӳ�������������ؼ��ɽ�ȥ����ÿ�����������ܹ����в��ԣ�������������⡣���⣬������� �ԶԽṹ�������һЩ���飬���ƴ���Ч�ʺ�/���������ܣ���Щ����/Ӳ��Ȩ�������Ӳ����ƹ����м���ɡ�

��������ϵ�Ϳ�������

Altera�������Ϊ��������Nios��������ϵͳ�ʹ���������һ������Ҫ������������Ʒ���죬Altera������Ƕ��������ŷ��ؽ����µĴ����� ���µ�������̡���������ȷ������Ƕ��������Ƿ�����µ�ָ�������C��ΪǶ����Ƶ���ʵ������һ����Ҳӭ�ж��⡣Altera��Cygnus���� ��RedHat���У����к�������ָ���ϵ������Cygnus���Ժ����ص�����Ż����ǵ�GNUPro Toolkit�����Ǿ�������߷dz���Ϥ�ı�GNU������

������̳�Ϊ�������⡣�ֳɵ��������ṩ�˶�����ȷ�������飬�������̼� �ɴ����������衣�����ô���������������д���������ϵ������洢��ӳ��ͷ����ж����ȼ����dz����ɵ���ɸ���Ĺ�����Altera����SOPC�����ƻ� ����Ƕ������ߣ�����������������������С�����պܵ͡�

Nios II���ɿ�������

Nios II���ɿ�������(IDE)��Nios IIϵ��Ƕ��ʽ�������Ļ��������������ߡ�������������������Nios II IDE����ɣ������༭������͵��Գ���Nios II IDE�ṩ��һ��ͳһ�Ŀ���ƽ̨����������Nios II������ϵͳ������ͨ��һ̨PC����һƬAltera��FPGA�Լ�һ��JTAG���ص��£�����������Ա���ܹ���Nios II ������ϵͳд������Լ���Nios II������ϵͳ����ͨѶ��

Nios II IDE���ڿ���ʽ�ġ�����չEclipse IDE project�����Լ�Eclipse C/C++ �������ߣ�CDT�����̡�

Nios II IDEΪ���������ṩ�ĸ���Ҫ�Ĺ��ܣ�

(1)���̹�����

Nios II IDE�ṩ������̹������ӿ�Ƕ��ʽӦ�ó���Ŀ������ȡ�

�¹����� ——Nios II IDE�Ƴ���һ���¹����������Զ�����C/C++Ӧ�ó��̺�ϵͳ��̡������¹������ܹ����ɵ���Nios II IDE�д����¹��̡�

��������ģ��——���˹��̴�����Nios II IDE���Թ���ģ�����ʽ�ṩ����������ʵ����������������ʦ�����ܿ��ٵ��Ƴ������е�ϵͳ��

(2)�༭���ͱ�����

Altera Nios II IDE�ṩ��һ��ȫ���ܵ�Դ����༭����C/C++������

�ı��༭��——Nios II IDE�ı��༭����һ�������ȫ����Դ�ļ��༭������Щ���ܰ������������ʾ - C/C++�����븨��/����Э����ɡ�ȫ����������ߡ��ļ��������㷺�����߰�������ͽ̡̳����븨�������ٶ�λ�Զ����������õ��Թ��ܡ�

C/C++������——Nios II IDEΪGCC�������ṩ��һ��ͼ�λ��û����棬Nios II IDE���뻷��ʹ���Altera��Nios II���������������ף����ṩ��һ�����õİ�ťʽ���̣�ͬʱ����������Ա�ֹ����ø�����ѡ�

Nios II IDE���뻷���Զ�������һ�������û��ض�ϵͳ���ã�SOPC Builder���ɵ�PTF�ļ�����makefile��Nios II IDE�б���/�������õ��κθı䶼���Զ�ӳ�䵽����Զ����ɵ�makefile�С���Щ���ÿɰ������ɴ洢����ʼ���ļ���MIF����ѡ��������ݡ��� ������ʼ���ļ���DAT/HEX���Լ�profile�ܽ��ļ������ѡ�

(3)������

Nios II IDE����һ��ǿ��ġ���GNU����������֮�ϵ�������������GDB���õ������ṩ������������Թ��ܣ��Լ�һЩ�ڵͳɱ��������������в��ᾭ���õ��ĸ����Թ��ܡ�

�������Թ���——Nios II IDE�������������µĻ������Թ��ܣ����п��ơ����ö�ջ�鿴�������ϵ㡢��������鿴��������Ϣ�鿴��ָ���������

������ ——���������������Թ���֮�⣬Nios II IDE��������֧�����¸����Թ��ܣ�Ӳ���ϵ����ROM�������еĴ��롢���ݴ�����ָ����١�

(4)��������

ʹ ��Nios II����������ƶ��ڵ����ϲ��������棬���������洢FPGA�������ݺ�/��Nios II������ݡ�Nios II IDE�ṩ��һ������������̷������κ����ӵ�FPGA�ļ���ͨ������ӿڣ�CFI������������������ͨ��Nios II IDE�����������սᡣ��CFI����֮�⣬Nios II IDE���������ܹ������ӵ�FPGA���κ�Altera���������������б�̡�

ModelSim SE 6.1F (���ӷ���):

http://www.9iv.com/down/soft/1488.htm?eid=217990

http://lib.verycd.com/2006/06/02/0000105276.html

2006.6�³����е����°汾��ModelSim SE 6.1f

ModelSimרҵ��,VHDL��Verilog��Mixed-HDL������

Mentor Graphics ModelSim SE 6.1b��ҵ���������HDL���Է����������ṩ���Ѻõĵ��Ի�������Ψһ�ĵ��ں�֧��VHDL��Verilog��Ϸ���ķ����������� FPGA/ASIC��Ƶ�RTL�����ż���·�������ѡ��������ֱ���Ż��ı��뼼����Tcl/Tk�������͵�һ�ں˷��漼������������ٶȿ죬����Ĵ��� ��ƽ̨�أ����ڱ���IP�ˣ����Ի���ͼ�ν�����û��ӿڣ�Ϊ�û��ӿ�����ṩǿ�������ֶΡ�ȫ��֧��VHDL��Verilog���Ե�IEEE ����֧��C/C++���ܵ��ú͵���

���п��ٵķ������ܺ����Ƚ��ĵ���������ȫ��֧��UNIX(����64λ)��Linux��Windowsƽ̨��

��Ҫ�ص㣺

RTL���ż��Ż������ر���ṹ����������ٶȿ죻

���ں�VHDL��Verilog��Ϸ��棻

Դ����ģ������֣���Ŀ������

���������ܷ��������αȽϡ����븲�ǵȹ��ܣ�

������ChaseX��

Signal Spy��

C��Tcl/Tk�ӿڣ�C����

Synplify Pro 8.1

http://www.9iv.com/down/soft/1489.htm?eid=217990

Synplify Pro 8.1�뵼����Ƽ���֤������Ӧ��Synplicity��˾���ն���ɱ��������(PLD)�ۺ�����Synplify Pro 8.1�����˸Ľ���Synplify Pro����֧��Verilog-2001���Լ����������²���ϵͳ(OS)�����°汾��Synplify Pro���������������QoR(���ս������)���Լ���Ч��ʱ���漰�Զ��Ĵ������¶�ʱ���ܵ���ǿ���ܹ���������Ա�IJ����ʣ��������ܸ��ѡ�

ҵ�����ȵĻ���FPGA��ASICԭ����֤�ۺϹ��ߣ�ͨ���ṩ�����Ŷ���ơ��Զ�re-timing�����ٵı����� ��������������Ż���ƽ�������˾���B.E.S.T.�����⣬Synplify pro�ּ�����D.S.T.(Direct Synthesis Technology),SCOPE(Synthesis Constraint Optimization Environment),STAMP�Ͷ���Ż��ȼ�������������ߵ�����Synplify pro�ṩ�˺Ͳ��ֲ��߹���֮���native-link�ӿ������Push-Button�����̣�ʹ�û�ֻ��Ҫ����Ϳ���������е��ۺϺͲ��ֲ��ߵĹ� ��������Synplicety��˾��B.E.S.T.���棬Synplify Pro���������ۺ��������ŵ���ƶ�����Ҫ�ָ

Synplify Pro��ϸ��������

�� �ṩ���ڴ�ͳ�ۺϼ����Ŀ��ٵ�ȫ�ֱ�����ۺ��Ż����������ģ�������·���ĸ����ܺ���������ʵ��Ż���

�� �ṩ�����Լ����ȫ����ƣ����ܻ��˻����棬������Ч�ʣ���Ͼ��������ṹ���ṩ������ܣ�

�� �ṩ�Զ���RAM�������̣��ṩ�Զ�ʱ�ӿ��ƺ�ͬ��/�첽����Ĵ����ṹ���Զ�ʶ��FSM��ѡ����뷽ʽ�Դﵽ������ܣ��ṩ���FSM�Ŀ��ٵĵ��Ժ۲칤�ߣ��Զ�������ˮ����������ߵ�·���ܣ�

�� �ڲ��ı�ԭ���������£��ṩ�ڲ��������ⲿ���Թܽŵ���������Դ���롢RTL��ͼ��Log�ļ�֮��Ľ�����ʶ������

�� ���ɻ���ͼ�λ��ķ����͵��Թؼ�·���Ļ�����

�� ֧�ֺں��ӵ�ʱ���Լ��ܽ���Ϣ��֧��ͬʱʵ�ֶ��Ӧ�ã�ͨ����ƻ���֧��Xilinxģ�黯��ƣ�

�� �Զ�����������мĴ���ƽ����������ܣ�֧�����ܻ��������ۺϡ�

Synplicity Amplify V3.6.1 (���������Ż���):

http://www.9iv.com/down/soft/1069.htm?eid=217990

�� ��һ��ΪFPGA��Ƶ������ۺϲ�Ʒ�� Amplify Physical Optimizer ��Ʒ���������е�Synplify FPGA�ۺϲ�Ʒ����ͨ�����ۺϹ����г���������������Ϣ��������ܺ���������Amplify Physical Optimizer��Ϊ��Щ��Ҫ�����ǵ�Xilinx Virtex?ϵ�к�Spartan-3 ϵ�������л�þ����ܵ���ߵ����ܵĿ�����Ա�����ġ� Amplify��Ʒ�Ѿ���ȫ��100�����ҵ���á� Amplify?���߽���˼Ĵ�������RTL����ͼ������Լ���Լ����µĿ�ͬʱ��ɲ��ֺ����Ż��������ۺ��㷨�������������һ������Ƶ��������֣� ������һ���µ������Ż������������⣬Amplify��Ʒ��������ȫ����Optimization Physical Synthesis (TOPS)������ TOPS������һ�����������ܣ�ͬʱ��ͨ���߶�ȷ��ʱ����㽵������Ʒ���������

Mentor Graphics LeonardoSpectrum V2005a.82 (HDL���ۺ�����):

http://www.9iv.com/down/soft/2019.htm?eid=217990

LeonardoSpectrum��Mentor��˾��Ʒ��һ��HDL���ۺ�����������LEONARDO SPECTRUM������������VHDL����Verilog����,LeonardoSpectrum����Mentor Graphics��չ�����������dz����㣬���߱�����վ�ȼ�ASIC���ߵď���������������Ż�������ɫ��

LEONARDO SPECTRUM�Ƿdz��õ����ۺ����������� LEONARDO SPECTRUM������������VHDL����Verilog���Խ���PLD��FPGA��ASICԪ����LeonardoSpectrum����Mentor Graphics��չ�����������dz����㣬���߱�����վ�ȼ�ASIC���ߵď���������������Ż�������ɫ��LeonardoSpectrum�ṩ PowerTabs�˵�������ʦ��������սʱ����ʹ�����е��Ƚ��ϳɿ���ѡ�����֮�⣬LeonardoSpectrumҲ��������ĵ��Թ��ܺ�ҵ�� ���е���·�̽��������five-way cross-probing����ʹ�����������Ƶķ�����ϳɡ�

Mentor Graphics Leonardo Spectrum�ṩ���õĺϳ�����

Leonardo Spectrum��Mentor Graphics��չ�ĺϳɹ��ߣ�����Э��Atmel�ͻ���һ���ϳɻ�����ʹ��VHDL��Verilog�������FPGA��ƣ���������Թ�ҵ���ơ�ͨ �š���Ƶ���������ý���Ӧ���г��������Ľ�������FPSLIC��ơ�LeonardoSpectrum�IJ����dz�����֧�ָ��ָ�����Ʒ�ʽ���� ����Ա�ɾ��ܿ������ǵ�FPGA��ƣ�����������ƽ�����������ǵ������������

LeonardoSpectrum��Mentor Graphics���ӹ�˾Exemplar Logic��רҵVHDL/Verilog HDL�ۺ������������ã��ɿ��Խ�ǿ��������LeonardoSpectrum���ۺ��Ż�������EDIF�ļ�����ΪQuartusII�ı������롣���� �����������ۺϷ�ʽ��Synthesis Wizard���ۺ�����Quick Setup��������ɣ���Advanced FlowTabs����ϸ���̣���ʽ�����ַ�ʽ��ɵĹ��ܻ�����ͬ��Synthesis Wizard��ʽ���Advanced FlowTabs��ʽ����ȫ�棬�÷�ʽ������ѡ�����ͼ��ʾ���ֱ�������¹��ܣ�����ѡ������ļ����롢Լ������ָ�����Ż�ѡ����������ļ����ü� ѡ����ò��ֲ��߹��ߡ�

����ÿ���������ṩ��Ӧ�İ����������ˡ���Ҫע����ǣ�����������ļ�ʱҪ��ȷ�����ļ��Ĵ����ײ��ļ�����ǰ�棬�� ���ļ��ŵ����棬����LeonardoSpectrum����������ȷ�ؽ���������Ϣ�⡣�ۺ���ɺ��Խ���������ļ� ��.EDF����ΪMAX+PLUS II��Quartus II����������ļ�������ɱ��롢���桢��ʱ������������̵Ȳ��裬�������ϵͳ����ƹ��̡�

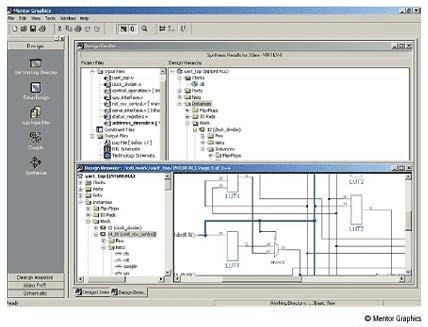

Mentor Graphics FPGA Advantage 7.2 (FPGA���):

http://www.9iv.com/down/soft/2715.htm?eid=217990

Mentor Graphics�߶���ƹ���FPGA Advantage!����ƴ��������桢�ۺϵĸ�������������ƵĹ���������������ֶΡ�����桢 �����ۺϵȣ�FPGA 7.2��һ�����ߵ�����!

FPGA Advantage For HDL DesignΪFPGA����ṩһ�������õ��������������������ƵĴ�����������֤���ۺϡ����ֲ����Լ��ĵ�����ƵĹ���������Mentor����ǿ�� �Ĺ��߽��ܽ����һ��HDL Designer Series����ƴ������ĵ�������ModelSim�����棻Leonardo Spectrum���ۺϣ���ҵ��Ψһ��FPGAȫ������ƹ��ߡ�FPGA Advantageʹ����FPGA��ƻ�����ǿ����������������������

�ٷ���ַ��http://www.mentor.com/products/fpga_pld/fpga_advantage/index.cfm

Mentor Graphics ��˾���

Mentor Graphics® �ǵ�������Զ����������쵼���̣����ṩ������������Ӳ����ƽ���������ÿͻ����ڶ�ʱ���ڣ�����͵ijɱ������г����Ƴ�����ǿ��ĵ��Ӳ�Ʒ�������·�� ��뵼��Ԫ����ø��Ӹ��ӣ��������������ռ�����ϵͳ��оƬ�������Ӧ�ã�Ҫ��һ�����д�����뷨ת�����г��ϵIJ�Ʒ�����е����Ѷ��Ѵ�����ӣ�Ϊ�� Mentor�ṩ�˼������µIJ�Ʒ����������������ù���ʦ���Կ˷����������ٵ������ս��

Mentor Graphics Precision RTL Synthesis v2005b (EDA�ۺ���):

http://www.9iv.com/down/soft/2018.htm?eid=217990

Mentor Graphics Precision 2005b.91 ���°棬���:

Mentor Graphics Precision RTL Synthesis��ӦFPGA��չ����һ��RTL�ۺ��������зdz�ֱ�۵Ľ��桢ȷ��ʱ��������Ƚ����Ż��㷨����ͬʱ���������ƽ�����������ʱ�� ��Ҫ��SDC��ʽ��ʱ��Լ�����Ͼ�ȷ��ʱ����������Ż�����������ս�Ե���ơ����ö��ص�ASE�Ż��㷨���Զ�ʵ��״̬�������κͶ������������ ��������ʽ��ȷʱ�������Լ��������֤�����Ľ�������ɵ�ԭ��ͼ������չʾ�ۺ����̺�������Դ�����ò���ѯ�ؼ�·����

Mentor����Precision RTL����ʵ��FPGA��ASIC��ת

Actel��˾��Mentor Graphics��˾���������Ƴ����°汾Mentor Graphics Precision RTL�ۺϹ��ߡ��ݽ��ܣ��ù������������ʦ��ʹ��Actel��FlashΪ�����ϵ缴��ProASIC Plusϵ���ֳ��ɱ��������(FPGA)����������д���������ܡ�����ǰ�������汾��ȣ�ʹ��Precision RTL�ۺϹ��ߵĿͻ�Ԥ�ƿ�����ʱ��Ƶ��ƽ����18%��Precision RTL�ۺϹ�������ȫ������Actel��Libero 6.0������ƻ���(IDE)�У��������Ա���趨���ߵ�Ƶ�ʣ����������е����������ʵ�ָ��ߵ�ProASIC Plus��������������

�ݽ��ܣ��˹��߾���Actel�IJ��ԣ�����30,000������Ԫ�Ķ�����ƣ����֤����߿��������ʱ��Ƶ�ʡ�Precision RTL�ۺϹ�����ͨ�������ض��Ľṹ�㷨������ǿ��ȷ��ʱ�������ۺϼ����Ͳ��ö����Ż�������ʵ�ֵġ�

Precision RTL�ۺϹ���Ϊ���ӵ�FPGA��������һ��ո�·����Ķ��塣�ù�����ͳһ������ģ�ͣ��������Ա���ж�ǶȵĽ���̽�⣬�Ա��ڷ������ʱ���õؽ��� ���ơ���ֱ�۵ĵ��Ի�����������ʱ��������ߣ��������ͻ�������һ��FPGA��ʵʩ��ʱ�������ս���Ӷ�����������ڲ�������ܡ�

ProASIC Plusϵ������ϵͳ���ܶ���75,000��100���ϵͳ��֮�䡣ProASIC Plus����ϸ�����͵�оƬ����ASIC�ܹ������ʧ��Flash���ô洢����һ������ר�ü��ɵ�·(ASIC)����Ŀ�ѡ��������Щ����ӵ����ASIC ��ͬ�����ԣ����ϵ缴�����С����ģ���߸߶Ȱ�ȫ�Լ����������̼�������������������������ô洢����ProASIC Plus�Ľṹ����Ʒ���֧�����е�FPGA��ASIC�������̣������̲�Ʒ����ʱ�䣬�������Ա��FPGA��ASIC����֮��ת�ơ�

Mentor Graphics Precision RTL��Ҫ�ص㣺

��ƽ��������̲���������

���ɶ������������Ľӿڣ�

֧��VHDL��Verilog��EDIF��������ϣ�

ASE�Ż����Ĵ����ض�ʱ�������ۺϣ�

��ʱ�ӡ��첽ʱ�ӷ���

What-ifʱ�������

δԼ������

Mentor Graphics HDL Designer 2005.2 (�����Զ�������):

http://www.9iv.com/down/soft/1073.htm?eid=217990

��ƴ��������̹���ϵ�й���,10�·����·���!

HDL Designer SeriesΪ������Ч�ʺ���������ṩ�������ױȵ�����ֶκ��ܡ�ͨ��ͼ�λ����ı������ߵ���ϣ����IP�����룬���ٸ�Ч�Ĵ�����ƣ�HDL���� ����ͳһ��HDL�����ĵ��������汾����Ϊ�Ŷ�����ṩ�˻�����ȫ���VHDL��Verilog��mixed-HDL֧����Ӧ�����ŵ�FPGA�� ASIC��SoC��ơ�����湤����ModelSim���ۺϹ�����Precision����ṩ������FPGA/ASIC������̡�HDL Designer Series���������ĸ�ϵ�в�Ʒ��

HDL Pilot��ƹ������ߣ�

HDL Author ��ƴ������ߣ�

HDL Detective��Ʒ��������ӻ����ĵ��������ߣ�

HDL Designer���������������ߵ����й��ܡ�

Mentor Graphics HDL Designer 2005.2�ӿ츴��оƬ��Ƶ����������

Mentor Graphics HDL Designer ��������Ϊ�ͻ��������������ߵ�������롢������������ܣ�������ǿ����������ϱ���������Ƹ�������Σ�����Ѹ�ٽ�����Ʒ���ҽṹ���õ�Ӳ�������� �ԡ�HDL Designer Series��Э������ʦѸ������ͷ������ӵ�ASIC��FPGA��ϵͳ��оƬ��ƣ��ÿͻ��²�Ʒ�ڸ���ʱ�������С�

Mentor Graphics��˾HDL Designer Series�����ܼ�Valerie Rachko��ʾ��������ƹ���ʦ���ú���Ӳ����������Ʒ�����HDL Designer Series��������Ϊ�����ṩһ��������ҵ������ʹ�������������Ӳ������������ơ�����������ʵ��Ӧ�ý��֤��������Interface- Based Design™���ڵĶ�����ɫ�ø�����·��������Ϊ��һ�����㹤��ʦ����������°汾����ǿ���ļ���¼����ʾ����������ƹ������ܡ�

�Խ���Ϊ������IBD��Ʒ����ø�����Ƶ���·��������Ϊ������·��Ƹ����Խ���Ϊ������Interface-Based Design��IBD™����Ʒ������ùۿ�����ľ����������ʾ��·�ṹ���������༭����������ƹ���ʦѸ��ָ���ź���·��Ȼ�������Ӧ��VHDL�� Verilog�ṹ������ʹ�����������Թ��ܷ���ͼ����ʽ���ۿ�IBD�������ϡ�

Ϊ֧��IBD��Ʒ�����HDL Designer Series 2004.1�ṩ�˶����¹�����ɫ��������

�� �����ɾ����·�������Ľ�����������ײ�ܹ�

�� �����ɾ��ijЩ�ײ㣬�Ա�����ײ�ܹ��Ľײ㰲�ŷ�ʽ

�� ��̬����IDB�빦�ܷ���ͼ���ڵĶ�Ӧ����

�� չ��������ָ���ı������У���ʹ�����趨�Լ�ϲ���Ĵ�����ʾ��ʽ

�� ���������ҷ���������������˳��

Debug Detective���ܼ�ǿ

Debug Detective™��HDL Designer Seriesӵ�и�ǿ���Ӳ���������Է���������ͬʱ�����ModelSim®������̵���������Debug Detective����ModelSim��ִ�У�����ͼ�λ��������ʾӲ���������Գ�����룬������ǿ��Ƴ���������

Debug Detective������ɫ�ͼ�ǿ���ܰ�����

�� ��ǿ���״̬����ִ�н����ʶ������rendering recognition��

�� �ɹ滮��̽����ʾ����

�� ���湤���к�ModelSim����ѡ���ṩ����ķ������ѡ��

�� ��Χ�����̽������Ϣ��force����

����HDL Designer Series

HDL Designer Series�Ĺ��ܺ����������������������в��棺HDL Pilot™�ṩ��ƹ�����HDL Detective™�ṩ��Ʒ������ļ���¼��HDL Author™�ṩ������ͼ�α༭�Լ��ļ���¼��HDL Designer™�ѵ��㹤�����й��ܺ�ǿ���ļ���¼������ϳɵ�һ���������Debug Detective��ѳ�������Ʒ��������ṩ��ModelSim������������HDL Designer Seriesͬʱ�ṩӲ������������ơ�������������ܣ��ǵ�������Զ�����ҵ�������Ĺ����������⣬HDL Designer Series��֧�����г��õķ�����ϳɹ��ߡ�

���� Mentor Graphics

Mentorӵ������һ���ĵ�����/Ӳ����ƽ��������Ϊȫ����ɹ��ĵ�����뵼�幫˾�ṩ�����Զ���ƻ��IJ�Ʒ����ѯ����ͬʱ��Ҳ�ǽ������Ȳ����� ���������������Э���ɾͽ�(STAR Award)�Ĺ�˾��Mentor������1981�꣬ȥ��Ӫ�ս���6����Ԫ��ȫ��Լ���� 3,100 Ա������˾�ܲ�λ���������ո���(Oregon)

Synplicity Certify 6.4 (FPGAԭ����֤):

http://www.9iv.com/down/soft/1065.htm?eid=217990

Synplicity��˾��ȫ������FPGA�����ASIC��֤������Ӧ�̣���ȫ��ʮ��EDA������˾֮һ����1995����������ȳ��� ������Ӫҵ��ÿ���Գ���80%����������ߡ���˾������������FPGA�ۺ�����----Synplify�ڹ�����Ϊ���ʦ��Ϥ��ʹ�á���������ʽ���� �й��Ժ����ŷ����뼼��֧�����ȵ���ߣ�����ʹ���ʦ����

SynplicityĿǰ��Ҫ��Ʒ��HDL�ۺϹ��ߣ�Synplify����HDL�ۺϹ��ߣ�Synplify Pro, HDL�����ۺϹ��ߣ�Amplify����ASCI��FPGAת������: Certify��

Synplicity��˾��Ʒ��Certify��RTL����Ƭ�ָ����ۺ�ASICԭ����֤�������������Ϊ����߸���оƬһ�γɹ��Ŀ����ԣ� CertifyΪ�ͻ��ṩ�����ö�ƬFPGAоƬ���ٶ���ϸ�ĵ��Ժ���֤���ģASICоƬ�Ľ��������Certify���Կ��ٵ���RTL������ԭ�ͣ��� ����FPGA��ʵ�֡�ͬʱ��Certify�ṩ���ͻ���ʵʱ���������ϵ�����Ӳ�������������⣬Certify�ּ�����DW���ſ�ʱ�ӵ�֧�֣��������� ��ƣ��ֳ���оƬ����оƬ��֤�Ͳ�����������

I-Logix Rhapsody 6.2 (Ƕ��ʽ���濪��)

���ص�ַ��http://www.9iv.com/down/soft/1100.htm?eid=217990

����http://lib.verycd.com/2006/01/04/0000083110.html

Rhapsody 6.2�߶�Ƕ��ʽ�������ߣ���2005.12���·�������ǿͼ�δ���������������棡��ΪǶ��ʽ�����Ŀ����ṩ��һ��“�Ļ�”��֧��ƽ̨�������ӻ��� ���̻����Զ������Ŷӻ������ṩ�˿��ӻ��Ŀ����������ᴩ�˹��̻������˼�룬ʹ�����Զ����Ŀ���ģʽ����֧���Ŷӻ���Э��������

I-Logix Rhapsody��ҵ������ʢ�����������Һ�����̫������(NASA)�Ļ���̽·�ߺ�������������Rhapsody��VxWorks�Ͽ���Ӧ�ó���

�ٷ���ַ��http://www.ilogix.com/homepage.aspx

The newest release of Rhapsody 6.1, offers a rich feature set to users with key enabling technologies that empower designers and developers to use SysML,

DoDAF, CORBA and in a natural, easy-to-use tool environment. Loaded with enhancements and new features to make a seamless and efficient environment for

systems, software and testability, the new tool family represents a “best of breed” solution to users.

���ݵ������ı��棬Rhapsody����Ѹ�ٳ�Ϊ����/���պ���������ѡ��MDD��ģ������������Model Driven Development��������������һϵ����Ŀ�б���Ϊ��Ҫ����������ʹ�ã���Joint Strike Fighter (JSF), Future Combat Systems (FCS) and F-22�ȣ�ͬʱ��ͨѶ��ҽ�ơ����������ѵ��ӵ�����Ӯ�ÿ��ٳ�����������

I-Logix��˾��Rhapsodyϵ�в�Ʒ��ʵʱǶ��ʽӦ����������ƺͿ��������˸����Ե��½���Rhapsody ��һ�ֻ���ͳһ��ģ����UML��Unified Modeling Language? �� �Ŀ��ӻ���̻�����ͨ�����еİ�UML������ͼӳ��Ϊ����Ŀ����������Եļ�����Rhapsody�ṩ����һ�����������ڸ���ʵʱǶ��ʽӦ�������ӷ����� ���һֱ������ʵ�ֺ��������ԵĿ���������Rhapsody���û���UMLģ�͵Ŀ���������ͨ�������ģ����ֱ�����ɸ������Ĵ��룬�����������Ĵӱ���ת �Ƶ���������������Զ�������������������Ч�Ĵٽ����ŶӺ������������������������ʺʹ����������������������Ŀ���ʱ�䣬���������������Զ����ķ� չ����.

ҵ�����ȵ�Rhapsody��һ��ģ�������Ŀ�������������UML2.0Ϊ������ʹ��С��ͬ����Ŀ���ܹ�ͨ�����ӻ� ��ģ�ķ�����������ơ�ʵ�ֺͲ����Լ��Ĺ���������������ʵʱǶ��ʽӦ�á�RhapsodyרΪǶ��ʽ�г�������������ƺ��Ż�������ʵʱϵͳ����Ϊ�� �壬ʵʱ����ϵͳ��֧�֣�����ϵͳ��ʵʱӦ��֧�֣��Ų���������̡���Ƽ��ĵ��ԡ���Ч�Ĵ����Զ����ɣ�C��C++��Ada��Java�����ĵ��Զ� ���ɵȡ��ͻ�����˵��Rhapsodyʹ���Ǵ�������˿������ڣ������ڳ���ʹ�øù��ߵ�����¡�

Rhapsody6.0�������汾����м���ͻ���ԵĸĽ���

����֧���������������������Ҳ֧�ִ�ͳ�������ֽܷ�Ľṹ�������� Rhapsody������������UMLʹ�������ܺ�����������Ƽ�����г������ͬһ������֮�С�

�����ʺ����������ߵ���Ҫ��Ҳ�ʺ���Ϊϵͳ��ƵĹ�����ʹ�á�

��C���Ե�֧�ֽ�һ��ǿ��������32λǶ��ʽӦ�û���8λ/16λӦ�ã������Ƿ���ʵʱ����ϵͳ��Rhapsody5.0���ṩǿ�����Ŀ����ֶΡ�

I- Logix����ϯ��ʦBruce Powel Douglass��ʿ�ڽ����������ʵ��ݽ��У�������Rhapsody�ļ�����Ҫ���ԣ���ȫ��ѭUML�������ص�ģ��/��������Լ����Լ�ͼ�λ��ġ��� �Ƽ��ĵ��Ժ���֤���������⣬Rhapsody����֧�ִ���Ŀ����������Ϣ��������Ҫ��ÿ���û���˽�й�����ά���Լ������ģ�ͣ�Rhapsody������ ���ģ��������ʽ�洢����Ŀ�ڣ����ṩ�����ͻ��ֹ��ܡ��Ŷ�֮�����ͨ����������ֱ�ӵ����Լ����е����ù�������ʵ��Эͬ������

UML����ʵ“����”

UML��ͳһ��ģ���ԣ��������������������������������OOAD����������������ƣ����ߵĽ�ϣ���ʹ��������˼���ʵ����ǰ����һ�� Rhapsody��ҵ���һ����ѭUML���Ե����������ƹ��ߡ��ܲ���������I-Logix��OMG�����������֯���ij�Ա�����Ҳ�����UML������ ����UML��1997��11�³�ΪOMG���ɵı���ģ���ԣ�Rhapsody��1998��2�¾Ϳ�ʼ�ṩ��UML��֧�֡�

��Rhapsody�У�����߿��Դ���UML֧�ֵ�9��ͼ��˳��ͼ��Э��ͼ����ͼ������ͼ������ͼ������ͼ��״̬ͼ���ͼ��ʵʩͼ��������ͼ�Ͷ���ͼ�� Rhapsody��ͳ��Ϊ����ģ��ͼ����ͬ��ͼ������ģ�͵IJ�ͬ���棬������ƹ��̡�Rhapsody���ṩ��һ����UML���Ԫ�أ��������첻ͬ�� UML���ͼ�������е�ͼ����ͬ������һ����ӳ��Ƶ�ģ�͡�

���Դ�������м������ģ�ͣ�Ҳ������ģ�ͼ�������ģ�͵�һ�����Լ������ȷ�ԡ�

��Ȼ�����ṩ���е�UML���ܣ���Douglass��ʿ�ڽ���Rhapsody��ʱ��ǿ����I-Logix���Ա�ֻ֤Ҫ��Rhapsody�ṩ�Ĺ��ܣ��� ��ѭUML������ijЩOOAD�����ṩһЩUML��֮���ר�й��ܡ�I-Logix��Ϊ���ṩһЩר�й���ģ����Ȼ�ḻ�˹��ߵ����ݣ��������� UML��ͨ�����ơ���ȫ��ѭUML��������ͳһ���Ļ����϶�Ƕ��ʽϵͳ������ȫ�ĺ;�ȷ�ķ�����

�Զ�����������

Rhapsody���û���ģ�͵Ŀ�����ʽ���ܴ����ģ��ֱ�����ɿ����е�Ӧ�ó���ͻ����ض�ƽ̨�ġ���Ʒ���ġ����������롣�����������Ĵӱ���ת�Ƶ�����ƣ���������������忪��Ч�ʡ�

��������ɿ�ܵ�����ص�����ģ�ͣ���������ԡ������ģ����Ϊͬһ��ƵIJ�ͬ��ͼ����ͬ���ڣ����ı���������һ��ʱ������һ��Ҳ��֮�Զ����£���ʹ�����ģ�����Ǻ�ʵ�ʴ���һ�¡�

Rhapsody�ṩ��150��������������ƴ�������ɣ����а������ɿ����г�����ض����ļ�����Դ�ļ���Makefile����ȣ���ָ������ij������ �ľ���Ԫ�ء���ִ���ٶȺʹ���ߴ�֮�����ȡ�ᡢָ�����ɴ���ķ��ѡ��ʵʱʱ�ӻ�ģ��ʱ�ӵȡ���Rhapsody�л����Խ�����ʹ�õ��������Ա����� �����Լ����ڲ�ͬ��Ҫ�����ɲ�ͬ����Ĺ��̡�Ҳ���ԶԴ������ɿ�ܽ������䣬�������ض����������Ĵ������ɻ��������̿������ڵ�ͬʱ������˴����� ����

��ΪRhapsodyר�����Ƕ��ʽ���������Զ�ʵʱ���ܵ�֧����������Ҫ��ɲ��֡�Rhapsody��ʵʱ����ṩ��һ��ΪʵʱǶ��ʽӦ��ר���Ż����� ��ģ�壬��ʵʱ��

���ĵ�ַ��http://www.45fan.com/a/question/69981.html